Over the past five years, EUV pattern design has made significant strides, but high-NA EUV has brought back the old challenges.

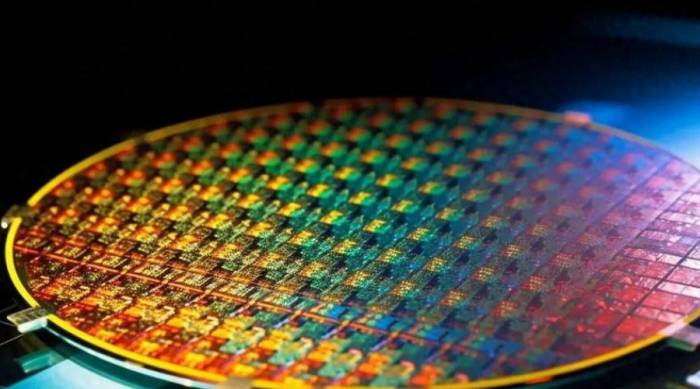

As semiconductor devices become more complex, so do their patterning methods. The extremely small feature sizes required for each new node demand constant advancements in lithography technology. Although the basic lithography process has remained unchanged since the industry's inception—illuminating a prepared silicon wafer through a photomask—the technology and methods in every part of the process have undergone tremendous changes. These advancements have accelerated as extreme ultraviolet (EUV) lithography technology has transitioned from the lab to large-scale production for 7-nanometer and 5-nanometer processes over the past five years. Now, with the impending arrival of high numerical aperture (high-NA) EUV, the debate between single-patterning and multi-patterning techniques for the 3-nanometer node and below has intensified.

The uniqueness of EUV multi-patterning lithography lies in the decision to use single-patterning or multi-patterning, which requires consideration of the required dose to expose the wafer and still be manufacturable. Single-pattern lithography may be more expensive than double-patterning processes because single patterns may require more than double the exposure dose and have worse throughput on very costly scanners compared to double-pattern processes.

Pushing the Limits of Single Exposure

Single exposure involves creating the desired pattern on the wafer using a single exposure step, reducing the number of process steps and associated costs compared to multi-pattern methods. This technique has long been favored by semiconductor manufacturers for its simplicity and cost-effectiveness. Some benefits of single exposure include:

Reduced defect risk: The risk of defects is lower with single exposure compared to multi-patterning, which may introduce alignment issues, overlay errors, and other defects that could affect yield. By minimizing the number of process steps, single exposure inherently reduces these risks, leading to higher yields and more reliable manufacturing outcomes.

Increased throughput: Multi-patterning requires several lithography and etching cycles, each extending the overall process time. In contrast, single exposure simplifies the manufacturing process, allowing for faster wafer processing.Reducing Costs: Each additional exposure in multi-patterning requires extra masks and increases the use of advanced lithography tools, thereby driving up costs. By reducing the number of exposures required, single exposure can significantly save on materials and equipment usage.

Simplifying Process Control: Managing process parameters and ensuring consistency across multiple exposures in multi-patterning can be challenging. Single exposure simplifies process control, making it easier to maintain consistency and repeatability in the manufacturing process.

Manufacturers have been working hard to make single exposure work because no one wants to do double exposure, which is too expensive. So this has indeed happened over the past five years. Companies have been pushing single exposure technology as much as possible, delaying the need for double exposure longer than anyone expected.

The gradual improvement in EUV scanner quality has played a key role in extending single exposure to ranges that were not possible when the ASML NXE:3400C scanner was first introduced five years ago. Since then, further advancements in power and scanner technology, including better lenses and more sophisticated illuminators, have helped reduce defect rates and improve yield. These improvements have increased the practical resolution of single exposure, making it a more viable option for smaller feature sizes.

ASML has introduced a series of 0.33 NA EUV lithography equipment models, and each time they do so, their throughput slightly increases, the overlay is better, and the lenses are better. Now they are shipping the 3800, with each model's reliability continuously improving.

The higher source power of ASML's latest EUV equipment allows for higher dosages, which in turn improves resolution and reduces the likelihood of defects. In addition, advancements in new photoresist technology have improved sensitivity and resolution, allowing for more precise patterning at smaller pitches.

In addition to improving the specifications of the EUV scanner itself, some techniques used in 193-nanometer dry and immersion lithography have also been applied to EUV to support tighter pitches. Many of these are resolution enhancement techniques (RET), source and mask optimization (SMO), more aggressive optical proximity correction (OPC), and even curve OPC, along with inverse lithography technology (ILT), whether Manhattanization or curve, for hotspots.

What was challenging at 32-nanometer pitch is now challenging at 30 nanometers, and what was challenging at 30 nanometers is now manageable at 28 nanometers. Although achieving true 28-nanometer pitch with single exposure is still difficult, improvements in EUV tool and resist capabilities have brought us closer.

However, despite the popularity of single exposure, it also has drawbacks. At smaller nodes, single exposure struggles to achieve high precision in finer pitches. As feature sizes shrink, the margin for error decreases, making it more difficult to maintain pattern fidelity and control defects. The randomness of photon absorption at these scales can also lead to variations that produce defects, and these issues become more severe as critical dimensions shrink. Moreover, the higher dosage required for single exposure at these smaller pitches can significantly increase the overall process cost and reduce throughput.

Manufacturers want to push single exposure as low as possible because it is more cost-effective. But it's not always that easy, as achieving good yield with single exposure often requires a higher imaging dose, and a higher dose increases costs. Now you have a higher-cost single exposure compared to a higher-cost double exposure, and understanding the exact trade-off point can become tricky.Patterning with Multiple Exposures

While single exposure offers several advantages, it also has clear limitations at smaller nodes. As feature sizes continue to shrink, the industry is increasingly turning to multiple patterning techniques to achieve the precision and fidelity required at advanced nodes of 3 nanometers and below.

Double patterning is inherently more complex and expensive than single exposure, but it is essential for achieving the smallest features at advanced nodes. It requires multiple hard masks and multiple exposures, but if you have a relaxed pitch and you are performing double patterning, you can use a lower dose, which means higher throughput per layer than single exposure. So there is a bit of cost offset.

The industry has been using immersion lithography for multiple patterning for many years, accumulating a wealth of knowledge about decomposing design layouts and self-aligned processes. The principles of multiple patterning are the same for both 193 immersion and EUV, but achieving the process control and precision levels needed to meet yield targets at the 3-nanometer node and below requires new strategies.

Process Control and AI

A significant challenge of multiple patterning is managing multiple exposures and ensuring that the overall performance of the final pattern meets the required specifications. Multiple exposures increase control difficulties, making it more challenging to maintain pattern fidelity and consistency. Additionally, using these techniques with expensive EUV tools further complicates the cost trade-offs.

Advanced lithography technology has over 1000 equipment and process parameters that need to be characterized and monitored to achieve quality results. This demand is accelerating the EUV development cycle, leading to the development of artificial intelligence (AI) systems that can optimize multiple patterning lithography and improve process issues such as overlay errors at these advanced nodes.

Furthermore, multiple patterning techniques such as Self-Aligned Double Patterning (SADP) and Self-Aligned Quadruple Patterning (SAQP) are necessary for the production of fine features required at 3 nanometers and below.

Self-Aligned Double Patterning (SADP) involves using a single lithography exposure, followed by a series of deposition and etching steps to create the pattern. The process typically begins with depositing a spacer material on the sides of pre-existing pattern features. This spacer is then used as a mask for subsequent etching steps, effectively doubling the number of features initially patterned by a single exposure.The Self-Aligned Double Patterning (SADP) EUV process can also leverage the high lithographic resolution of EUV to create very tight line-end spacing and other area-saving features required by designers. However, advanced manufacturing tools, such as inverse lithography technology (ILT), are needed to highly optimize the mask patterns and reduce the minimum size and spacing of circuit features on the wafer.

Self-Aligned Quadruple Patterning (SAQP) extends the principles of SADP to achieve even smaller feature sizes. SAQP involves additional spacer deposition and etching cycles, effectively increasing the pattern density of the original lithographic exposure by a factor of four. This approach is particularly suitable for creating the extremely fine spacing required for 3-nanometer and below.

The industry has been using immersion lithography for multi-patterning for many years, accumulating a wealth of knowledge about decomposing design layouts and self-aligned processes. These technologies and lessons learned can be reused with EUV lithography. It's not that EUV has any new tricks. Instead, as we move towards smaller dimensions, the demand for higher levels of process control and precision becomes more critical.

EUV Mask Innovations

Over the past five years, the infrastructure and technology for EUV mask manufacturing have improved significantly to meet the stringent requirements of the 7-nanometer and 5-nanometer nodes. The adoption of EUV lithography technology has driven the development of optical proximity correction (OPC) and ILT, which are essential for managing data volume and ensuring precise inspection of EUV mask features.

ASML has also made significant progress in improving the performance of EUV pellicles, achieving a transmission rate of 83% to 84%, significantly enhancing overall defectivity and transmission accuracy. The overall quality of EUV masks has also improved, making EUV lithography more suitable for mass production.

It seems that Hoya and Asahi Glass are now manufacturing enough defect-free mask blanks that people can actually consider exposure with certain types of masks. This was unimaginable a few years ago. Considering that producing a defect-free EUV mask blank was a significant milestone five years ago, the improvement in defect-free mask blanks is remarkable.

Curved Masks and Multi-Patterning

Curved masks have garnered significant attention for their potential to improve device performance and reduce power consumption. Curved features allow for more efficient designs, resulting in higher performance and lower power consumption in the final device. However, integrating curved features into the multi-patterning process still has a long way to go. The computational complexity of designing curved masks already requires GPU acceleration and AI support, and this complexity grows exponentially with the addition of multi-patterning.

Curved mask patterns were initially driven by curved ILT to achieve optimal resolution and process windows and were implemented by multi-beam mask writers. Since all EUV masks are written by multi-beam mask writers, they can also be curved. In particular, OPC is easily extended from segment-based Manhattan OPC to control point-based curved OPC, and companies are busy applying curved masks to EUV and DUV layers to shrink nodes and improve yield. The next requirement facing the industry is the need to extend ILT to full-chip or full-wafer curved ILT for EUV. Once an ILT product capable of full-wafer curved ILT for EUV is available, it will be adopted by the industry.One method of managing these complexities might be to keep the stitching boundaries as simple as possible, with the boundaries themselves having minimal complex features, and more complex curve features in the half-size reticle, similar to the approach taken in multi-chip modules. This method helps to maintain alignment and overlay accuracy, which is crucial for the success of multi-patterning at advanced nodes. It ensures that critical features are not affected during the stitching process, maintaining the integrity and performance of the final device.

Even if this is possible, it will still take some time to resolve the multi-patterning solutions with curve features. The lithography physics at these scales, including managing 3D effects and non-monochromatic light sources, adds tremendous complexity to the process.

High NA EUV

The introduction of High NA EUV lithography in the coming years will significantly impact the patterning field by providing higher resolution and improved pattern fidelity. High NA EUV technology is designed to reduce the need for multi-patterning, extending single exposure to 3nm and beyond. However, the transition to High NA EUV brings its own set of challenges, requiring substantial technical and financial investment.

The main advantage of High NA EUV is its ability to achieve finer resolution, pushing the boundaries of semiconductor manufacturing to the angstrom level. However, this increased resolution brings new challenges, particularly in managing stochastic effects and developing new resist materials that can withstand higher doses when patterning thinner layers.

For the 14-angstrom and 10-angstrom nodes, the industry will use High NA EUV, which requires double exposure stitching to manufacture large-size chips. High NA EUV will require innovative stitching and overlay control solutions, as well as advanced resist materials to cope with tighter process windows.

A major challenge facing High NA EUV is the development of suitable resist materials, primarily metal oxides. This shift from traditional chemically amplified resists to metal oxide resists is a significant change for the industry. While metal oxide resists offer improved performance due to their higher resolution and sensitivity at smaller nodes, they are not yet ready for mass production.

Nevertheless, the development of High NA EUV technology is progressing faster than expected. They have already imaged with these tools this past summer, which is quite remarkable. However, the high initial investment in High NA EUV infrastructure is a significant barrier, not to mention the ongoing costs of operation. Companies will have to weigh these costs against the potential benefits.

Conclusion

Over the past five years, EUV lithography has made significant progress, particularly in the field of single and double patterning. These advancements are crucial for the production of advanced semiconductor devices at smaller nodes. As the industry moves towards the adoption of High NA EUV tools, continued innovation and collaboration will be necessary to overcome new challenges and realize the full potential of these cutting-edge technologies.The ongoing debate between single and multi-patterning in EUV lithography highlights the dynamic nature of semiconductor manufacturing. At and beyond the 3-nanometer node, both methods will play a critical role, shaped by technological advancements and economic considerations.

Comments

Share your experience